計(jì)算機(jī)組成原理與體系結(jié)構(gòu)是軟件設(shè)計(jì)師必須掌握的核心基礎(chǔ)知識(shí),它直接影響軟件的性能、可靠性和可維護(hù)性。本文將從計(jì)算機(jī)組成原理的基本概念入手,探討其與軟件設(shè)計(jì)的密切關(guān)系,并分析在軟件設(shè)計(jì)過程中如何合理運(yùn)用體系結(jié)構(gòu)知識(shí)。

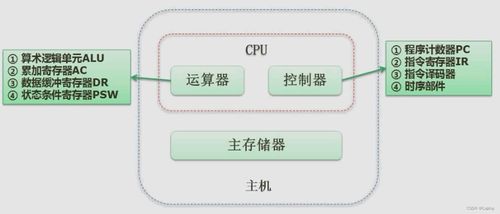

計(jì)算機(jī)組成原理主要研究計(jì)算機(jī)硬件系統(tǒng)的各個(gè)組成部分及其相互關(guān)系,包括中央處理器(CPU)、存儲(chǔ)器、輸入輸出系統(tǒng)等。而計(jì)算機(jī)體系結(jié)構(gòu)則更側(cè)重于計(jì)算機(jī)系統(tǒng)的抽象模型和設(shè)計(jì)方法,如指令集架構(gòu)、內(nèi)存層次結(jié)構(gòu)等。這些基礎(chǔ)知識(shí)為軟件設(shè)計(jì)師提供了理解計(jì)算機(jī)運(yùn)行機(jī)制的框架。

在軟件設(shè)計(jì)過程中,深入理解計(jì)算機(jī)組成原理與體系結(jié)構(gòu)能帶來(lái)多方面的優(yōu)勢(shì):

有助于性能優(yōu)化。了解CPU的流水線結(jié)構(gòu)、緩存機(jī)制和分支預(yù)測(cè)等特性,可以幫助開發(fā)人員編寫出更高效的代碼。例如,通過合理安排數(shù)據(jù)訪問模式,可以充分利用CPU緩存,減少內(nèi)存訪問延遲;理解指令級(jí)并行性可以指導(dǎo)循環(huán)展開等優(yōu)化技術(shù)的使用。

提高系統(tǒng)可靠性。掌握內(nèi)存管理機(jī)制、中斷處理原理等知識(shí),有助于設(shè)計(jì)出更健壯的軟件系統(tǒng)。特別是在開發(fā)操作系統(tǒng)、驅(qū)動(dòng)程序等底層軟件時(shí),這些知識(shí)更是不可或缺。

促進(jìn)跨平臺(tái)兼容性。不同的計(jì)算機(jī)體系結(jié)構(gòu)(如x86、ARM等)有著不同的指令集和特性,理解這些差異有助于設(shè)計(jì)出可移植性更好的軟件。

隨著多核處理器和分布式系統(tǒng)的普及,理解計(jì)算機(jī)體系結(jié)構(gòu)對(duì)于設(shè)計(jì)并發(fā)程序至關(guān)重要。了解緩存一致性協(xié)議、內(nèi)存屏障等概念,可以幫助避免并發(fā)編程中的常見陷阱。

在實(shí)際軟件開發(fā)中,軟件設(shè)計(jì)師應(yīng)當(dāng):

- 根據(jù)目標(biāo)平臺(tái)的體系結(jié)構(gòu)特點(diǎn)選擇合適的數(shù)據(jù)結(jié)構(gòu)和算法

- 考慮內(nèi)存訪問模式對(duì)性能的影響

- 充分利用硬件提供的并行計(jì)算能力

- 在性能關(guān)鍵部分進(jìn)行針對(duì)性的優(yōu)化

計(jì)算機(jī)組成原理與體系結(jié)構(gòu)知識(shí)為軟件設(shè)計(jì)師提供了從硬件角度思考軟件設(shè)計(jì)的能力,這種系統(tǒng)級(jí)的視角對(duì)于開發(fā)高性能、高可靠的軟件系統(tǒng)至關(guān)重要。隨著計(jì)算機(jī)技術(shù)的不斷發(fā)展,軟件設(shè)計(jì)師需要持續(xù)學(xué)習(xí)和更新這些基礎(chǔ)知識(shí),以適應(yīng)新的硬件架構(gòu)和技術(shù)趨勢(shì)。